# STCF Detector and Performance

### Jianbei Liu

**University of Science and Technology of China**

FTCF2025, Huangshan, China Nov. 24, 2025

## Requirements for STCF Detector

- ❖ Highly efficient and precise reconstruction of exclusive final states produced in 2-7 GeV e⁺e⁻ collisions

- ▶ High tracking efficiency (>90% @ 0.1 GeV/c) and high momentum resolution for low-p (<1GeV/c) charged particles, precise measurement of low-energy (<1GeV) photons.</li>

→ low mass tracking and PID detectors

- Excellent PID:  $\pi/K$  and  $\mu/\pi$  separation in full momentum range ( up to 3.5 GeV )

| Process                               | Physics Interest           | Optimized   | Requirements                                                           |  |

|---------------------------------------|----------------------------|-------------|------------------------------------------------------------------------|--|

|                                       | •                          | Subdetector | •                                                                      |  |

| $	au 	o K_s \pi \nu_{	au},$           | CPV in the $\tau$ sector,  |             | acceptance: 93% of $4\pi$ ; trk. effi.:                                |  |

| $J/\psi 	o \Lambda \bar{\Lambda},$    | CPV in the hyperon sector, | ITK+MDC     | $> 99\%$ at $p_T > 0.3$ GeV/c; $> 90\%$ at $p_T = 0.1$ GeV/c           |  |

| $D_{(s)}$ tag                         | Charm physics              |             | $\sigma_p/p=0.5\%,\sigma_{\gamma\phi}=130\mu\mathrm{m}$ at 1 GeV/c     |  |

| $e^+e^- \to KK + X$ ,                 | Fragmentation function,    | PID         | $\pi/K$ and $K/\pi$ misidentification rate < 2%                        |  |

| $D_{(s)}$ decays                      | CKM matrix, LQCD etc.      | PID         | PID efficiency of hadrons > 97% at $p < 2 \text{ GeV/c}$               |  |

| $	au 	o \mu\mu\mu, 	au 	o \gamma\mu,$ | cLFV decay of $\tau$ ,     | PID+MUD     | $\mu/\pi$ suppression power over 30 at $p < 2$ GeV/c,                  |  |

| $D_s 	o \mu \nu$                      | CKM matrix, LQCD etc.      | PID+MUD     | $\mu$ efficiency over 95% at $p = 1$ GeV/c                             |  |

| $	au 	o \gamma \mu,$                  | cLFV decay of $\tau$ ,     | EMC         | $\sigma_E/E \approx 2.5\%$ at $E=1~{\rm GeV}$                          |  |

| $\psi(3686) \to \gamma \eta(2S)$      | Charmonium transition      | ENIC        | $\sigma_{\rm pos} \approx 5 \ {\rm mm} \ {\rm at} \ E = 1 \ {\rm GeV}$ |  |

| $e^+e^- 	o n\bar{n},$                 | Nucleon structure          | EMC+MUD     | $\sigma_T = \frac{300}{100}$ ps                                        |  |

| $D_0 \to K_L \pi^+ \pi^-$             | Unity of CKM triangle      | EMC+MUD     | $\sigma_T = \frac{300}{\sqrt{p^3 (\text{GeV}^3)}} \text{ ps}$          |  |

Beam background at the inner most layer : ~1 Mrad/y, ~ $1 \times 10^{11}$  1MeV n-eq/cm<sup>2</sup>/y, ~1 MHz/cm<sup>2</sup>

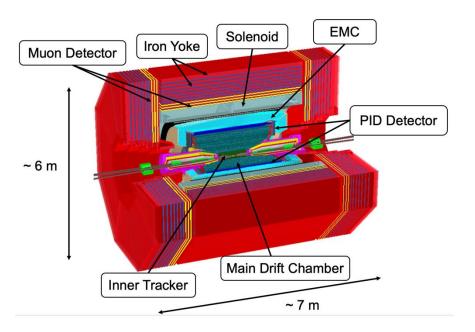

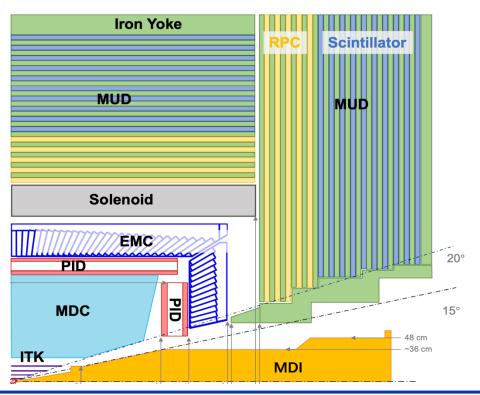

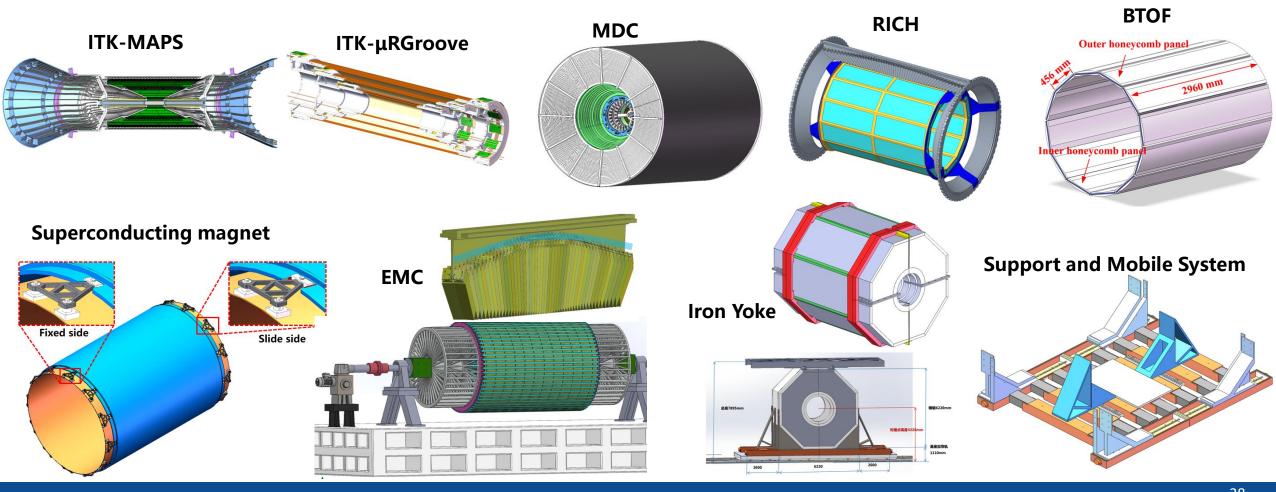

## **Updated Detector Design**

#### Main Performance requirements

Tracking: eff>90%@0.1GeV,  $\sigma_p/p\sim0.5\%@1GeV$

Energy meas.: 25MeV-3.5GeV

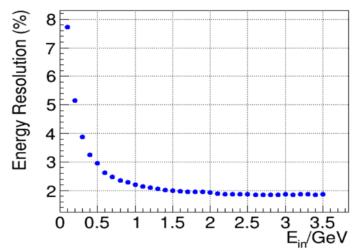

$\sigma_E/E \sim 2.5\%$  @ 1 GeV

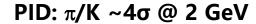

Hadron ID:  $\pi/K \sim 4\sigma$  @ 2 GeV,  $\sim 3\sigma$  @ 3 GeV

Muon ID: eff. >95%, mis-rate <3.3% @1 GeV

#### Inner Tracker (4 layers)

- MPGD: cylindrical uRGroove,  $\sigma_x \sim 100 \mu m$

- Silicon: low-mass MAPS, <0.3%X<sub>0</sub>/layer

- Main Drift Chamber ( $\sigma_p/p\sim0.5\%$  @ 1GeV)

- Small cells with helium-based gas,  $\sigma_x$  <130  $\mu m$

- PID System  $(\pi/K \sim 4\sigma @ 2 \text{GeV}, < 0.3 X_0)$

- Barrel: DIRC-like TOF BTOF ( $\sigma_t \sim 30 \text{ ps}$ )

- Endcap: RICH (<4mrad) or ASHIPH</li>

#### • EMC

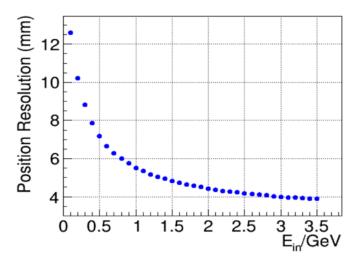

- pCsI + APD + waveform readout: ( $\sigma_E/E\sim2.5\%$ ,  $\sigma_x\sim5$  mm @ 1GeV &  $\sim1$  MHz/crystal )

- Solenoid: 1 T

- Muon Detector (eff. >95%, mis-rate <3.3% @1GeV)

- inner 5 layers : glass RPC, > 300 Hz/cm<sup>2</sup>

- outer 10 layers : scintillator strip + SiPM, ~ 2.4 m

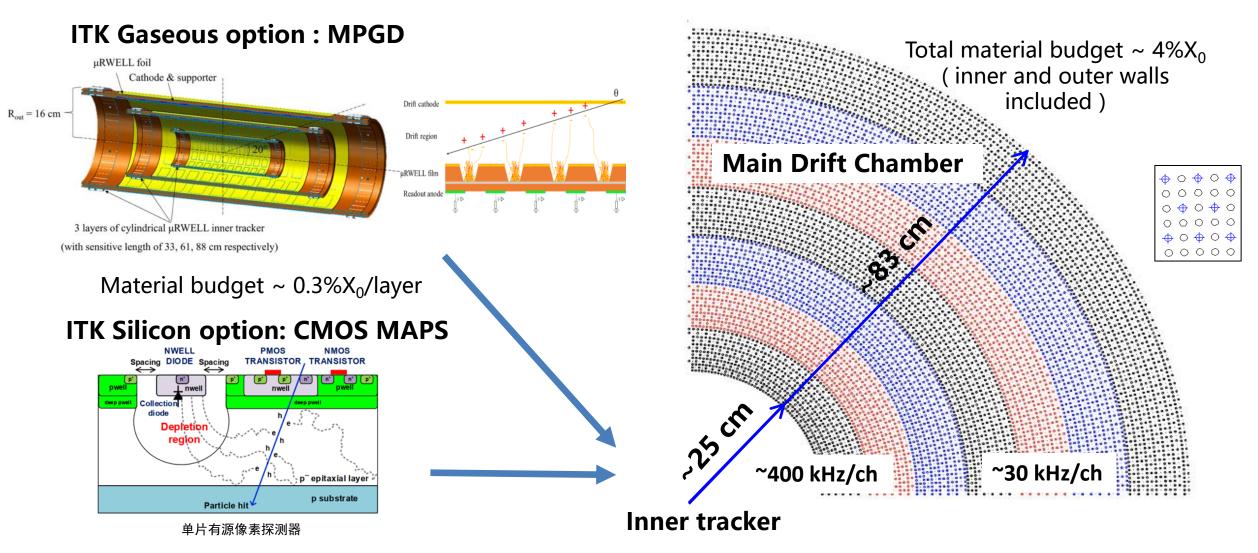

# Tracking System: ITK + MDC

Inner-outer separate designs to accommodate different levels of radiation background

# **Tracking System Layout Optimization**

| Layout<br>Options | Beam Pipe              | ITK                 | MDC                                                                            |

|-------------------|------------------------|---------------------|--------------------------------------------------------------------------------|

| CDR               | high material          | 3 layers, 36~168 mm | 48-layers, 20~80 cm                                                            |

| 1                 | budget                 | 3 layers, 36~168 mm | inner chamber with super small cells + 42 regular layers, 20~83 cm             |

| 2                 |                        | 3 layers, 36~168mm  | inner chamber with super small cells + 42 regular layers, 20~83 cm             |

| 3                 | low material<br>budget | 4 layers, 36~168 mm | inner chamber with super small cells + 42 regular layers, 20~83 cm             |

| 4                 |                        | 4 layers, 36~210 mm | 42 regular layers without inner chamber, starting with stereo layers, 25~83 cm |

- **❖** All the above detector geometries were implemented in OSCAR

- Full simulation and track reconstruction with Hough+GenFit were performed for benchmark physics processes to assess tracking performance

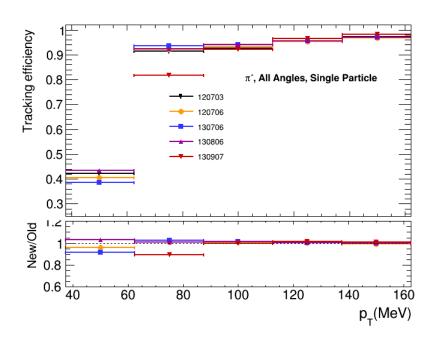

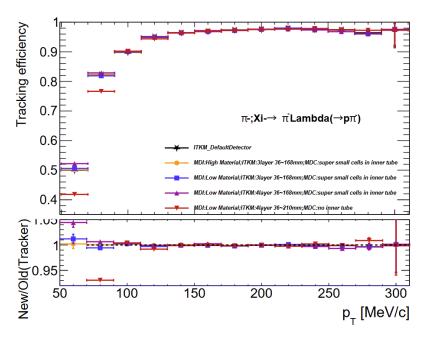

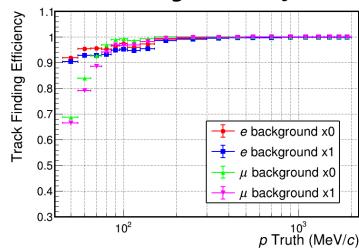

## **Tracking Performance with Different Layouts**

- **❖** Same tracking efficiency for different layouts when pt >100 MeV/c

- ❖ Important to have axial layers in the MDC inner part to maintain tracking efficiency for pt < 100 MeV/c with the baseline track reconstruction algorithm</p>

- ❖ The optimized tracker layout: 4 ITK layers + 42 MDC layers started with 10 axial layers. Detailed performance studies are underway.

- **❖** Further optimization of drift cell shape is underway (by BINP)

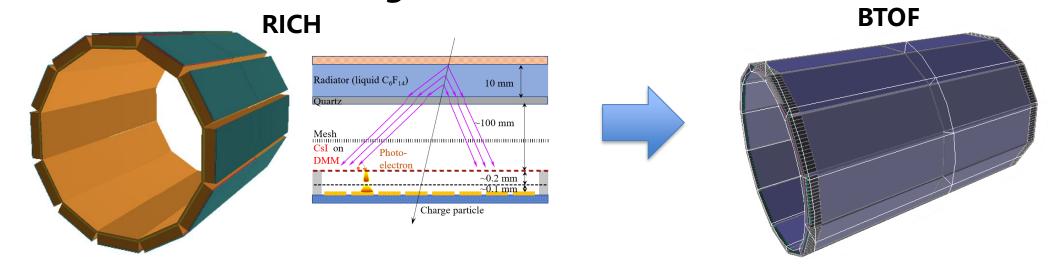

# **Evolution of PID Detector Options**

**❖** Barrel: baseline changed from RICH to BTOF

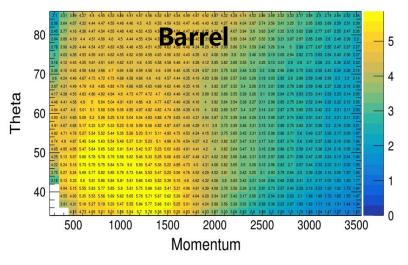

Endcap: RICH and ASHIPH in addition to the well-developed DTOF

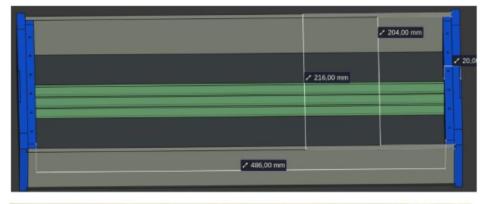

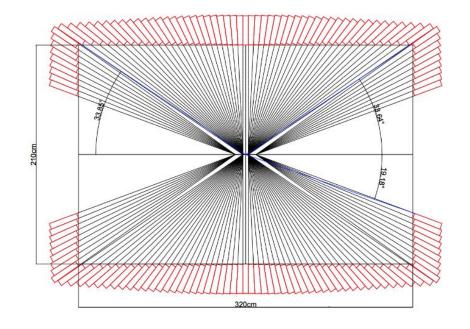

## BTOF: DTOF in Barrel (new baseline for barrel PID)

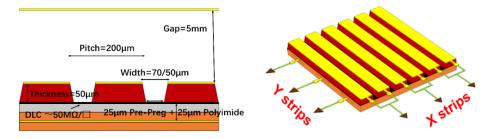

- Design of a barrel PID detector based on the DTOF technology (BTOF) has been developed

- 12 sectors with 2 modules placed longitudinally in each sector, 24 quartz plates in total

- Quartz plate parameters : R = 875mm H = 20mm L = 1350mm D = 450mm

- Quartz side plane is equipped with MCP-PMT for readout

- Performance assessed with full simulation, fulfilling PID requirements.

- Ongoing effort to optimize the design: bonding of BTOF modules, radiator thickness, optical filter (wavelength cut-off range), optical expanding volume ...

A lot of synergy with LHCb-TORCH is being explored

## **Muon Detector Optimization**

- A hybrid design with RPC (not sensitive to background) and scintillator strips (sensitive to hadrons) for optimal overall muon and neutral hadron identification performance.

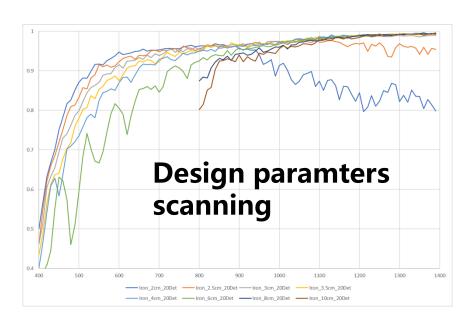

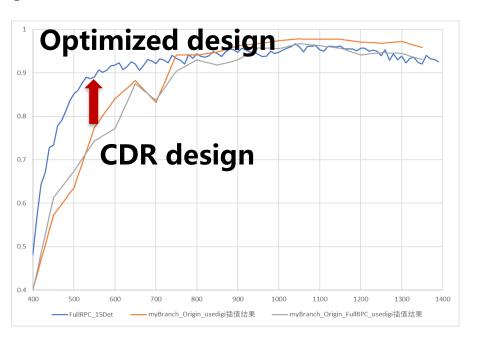

- Muon detector design has been optimized by scaning key design parameter: number of layers, iron absorb layer thickness, detector option combination

Optimized design: 15 detector layers (5 RPC layers + 10 scintillators layers) with 14 layers of iron yoke (2, 2, 2, 2, 2, 2, 3, 3, 3, 3, 4, 4, 5, 6, 10 cm in thickness)

## **Detector R&D Breakdown and Organization**

|    | System name             | Code | Participating Institutes                        |

|----|-------------------------|------|-------------------------------------------------|

| 1  | Inner Tracker - MPGD    | ITKW | USTC, IMP                                       |

| 2  | Inner Tracker - MAPS    | ITKM | USTC, SDU, CCNU, NPU                            |

| 3  | Main Drift Chamber      | MDCH | IMP, SDU, USTC, SZTU, BINP                      |

| 4  | Endcap PID Detector     | PIDE | UCAS, USTC, GXU, BINP                           |

| 5  | Barrel PID Detector     | PIDB | USTC, XIOPM                                     |

| 6  | EM Calorimeter          | ECAL | USTC, UCAS, SJTU                                |

| 7  | Muon Detector           | MUON | LZU, ZZU, SDU, USTC                             |

| 8  | Clock and Data Trans.   | CLDT | USTC, CNNU, HUST                                |

| 9  | Trigger System          | TRIG | USTC, HUST, SDU                                 |

| 10 | DAQ system              | DACQ | USTC, CNNU                                      |

| 11 | Forward System          | FWDR | ZJU, GXNU, USTC, LNU, NJU, DZU, Academia Sinica |

| 12 | Detector Magnet         | DSSM | SIEMENS SZ, IASF SZ, USTC                       |

| 13 | Mechanical System       | MECH | AUST                                            |

| 14 | Detector Control System | DCSS | USTC, IMP                                       |

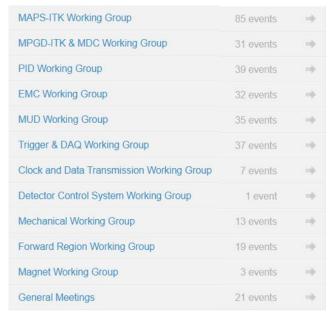

## Working Groups Meetings and Topical Workshops

Weekly or bi-weekly meetings for sub-working groups and detector group plenary meetings on a monthly basis. Mini-workshops on dedicated R&D topics.

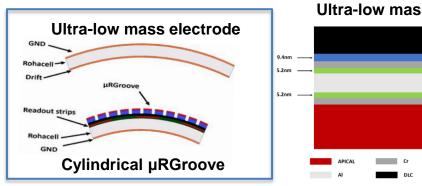

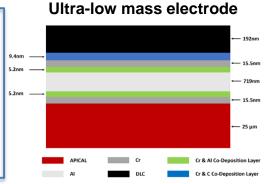

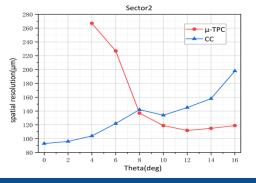

## MPGD ITK: µRGroove

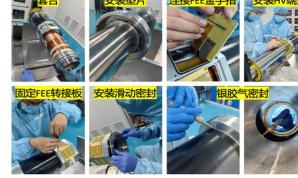

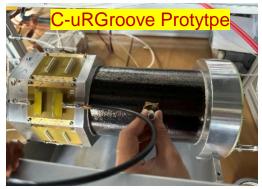

Proposed and developed a novel single-stage MPGD, micro-resistive Groove detector (µRGroove), for the inner tracker: larger signals and easier production compared to µRWELL.

Developed a set of techniques and procedures for fabricating a cylindrical low-mass µRGroove detector and built a low-mass c-µRGroove prototype: material budget ~ 0.23%X0/layer, the best in cylindrical MPGDs.

Conducted multiple beam tests of the prototype at CERN. Position resolution < 100µm for vertical tracks, and <130µm for inclined tracks or in 1T magnetic field.

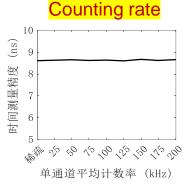

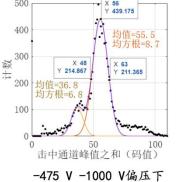

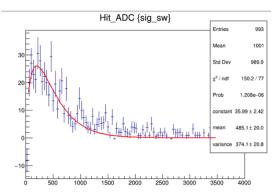

### **MPGD ITK:** Electronics

- ASIC is required for readout. Very challenging performance requirements (event rate much higher than VMM). Designed and produced a 32-channel prototype ASIC chip with full function, and tested it with a detector prototype.

- **Development of readout electronics with the ASIC** is well underway

| ASIC Specs       | Demands         |

|------------------|-----------------|

| Charge Range     | 40 fC           |

| Charge precision | $\sim$ 1 fC RMS |

| Time precision   | < 10 ns RMS     |

| Max. event rate  | 4 MHz           |

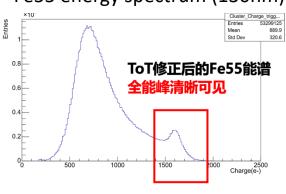

的能谱测量数据

-475 V -2000 V偏压下 的位置测量结果

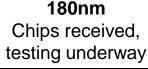

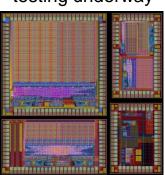

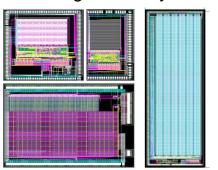

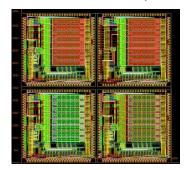

## **MAPS ITK: MAPS Designs**

- Core target: a low-power MAPS design with moderate position resolution and both timing and charge measurement capabilities.

- Low power outweighs position resolution: exploring strip-like or large-size pixel MAPS designs to reduce power.

- Exploring a super-pixel design that can provide both high position and high time resolutions for low power consumption.

Chips received, to be tested

Chips received. testing underway

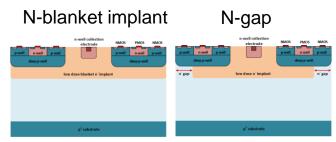

Supporting quadruple-well with possibility of N-blanket implant and N-gap. Chips received, to be tested

C: Pixel-based

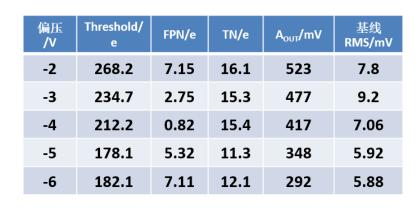

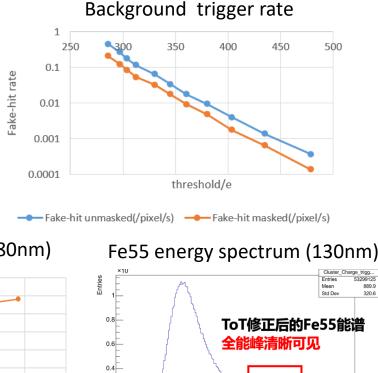

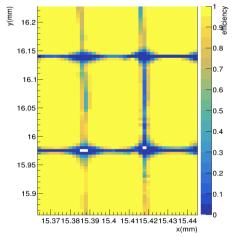

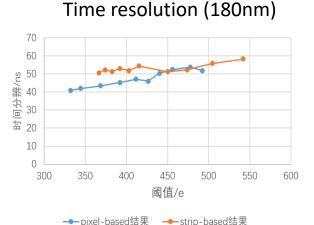

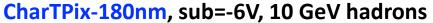

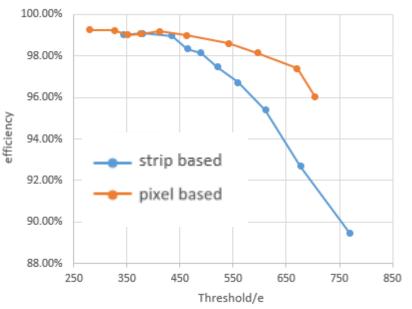

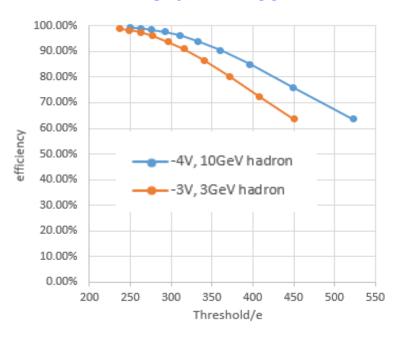

## **MAPS ITK: MAPS Testing**

Characterized the 180nm and 130nm chips for threshold, noise, fake hit rate and capacitance. Tested the chips with laser and radioactive sources (Fe55 and Sr90) for detection efficiency, charge collection efficiency and time resolution.

Efficiency

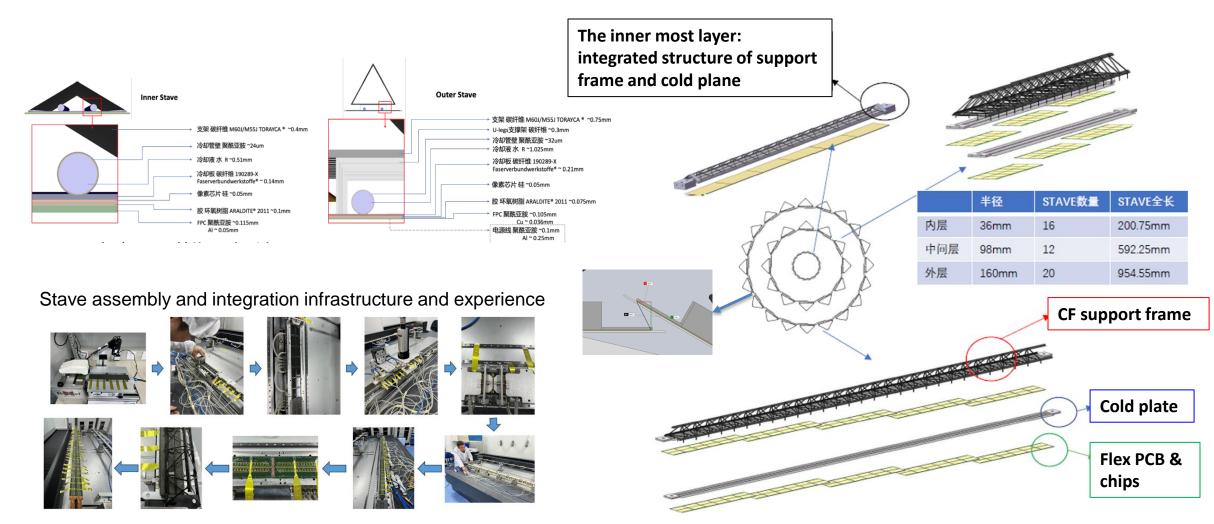

# MAPS ITK: Stave Design

Significant progress has been made in detector module (stave) mechanical design

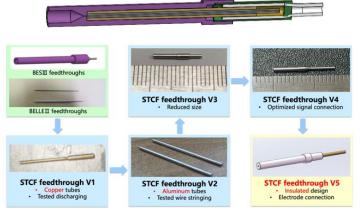

### **Main Drift Chamber: Detector**

- Endplate structure optimized to simplify the assembly process

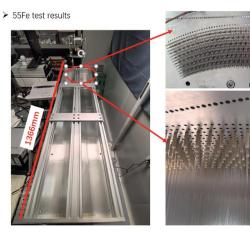

- Intensive R&D effort on feedthrough for super-small cells (~5 mm)

- A full-length super-small cell drift chamber prototype is under construction.

Layout of FEE boards

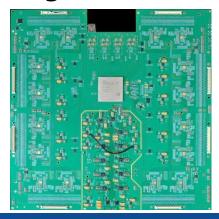

### **Main Drift Chamber: Electronics**

- The 16-channel electronics board (TIA + shaper + ADC) was updated with new passive components. After passing standalone tests, they are now ready for multi-board integration and testing with a detector.

- A new scheme of the electronics system was designed for more integrated layout and less material, separating the Front-End Electronics (FEE) and the waveform digitization board (WDM) on the MDC endplate.

- ASIC design is underway. Second version of the analogue part has been taped out and is being tested.

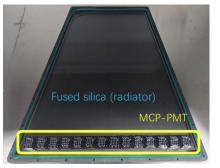

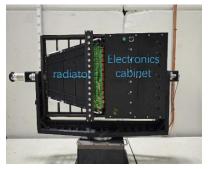

## **BTOF/DTOF Detectors**

■ A DTOF prototype was built and tested with particle beams at CERN to demonstrate the PID capability of the DTOF detector

π/K separation >4σ @ 2GeV/c

■ A full-length BTOF prototype has been built and tested with particle beams. Data analysis is underway.

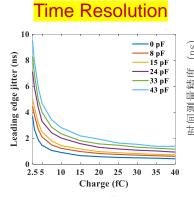

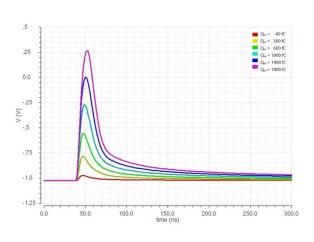

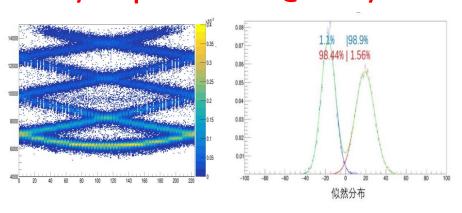

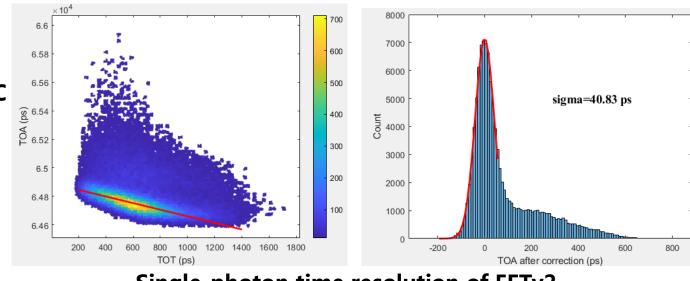

## **BTOF/DTOF Electronics**

- > ASIC FET v2

- 8-channel per chip, dynamic range 10 fC 1 pC

- RMS timing precision < 15 ps</li>

- Single-photon resolution 38–43 ps

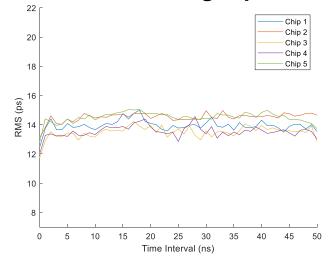

- > ASIC TDC: MCV-TDC v1

- 160 MHz system clock, LSB = 15 ps

- RMS precision 14 ps

- Event rate 32 MS/s

- Power consumption: 27.76 mW @5 MS/s

- > ASIC TDC: DSTA-TDC v2

- Taped out in mid-July 2025

- 8-channel per chip

- TA Gain = 16, LSB = 8 ps

- Adaptive elimination of time amplifier offset; Online calibration

Single-photon time resolution of FETv2

**Timing precision of MCV-TDC**

MCV-TDC and DSTA-TDCv2

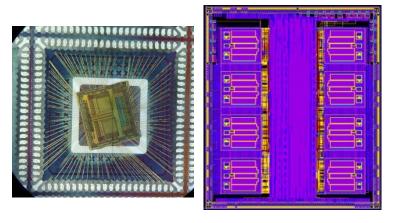

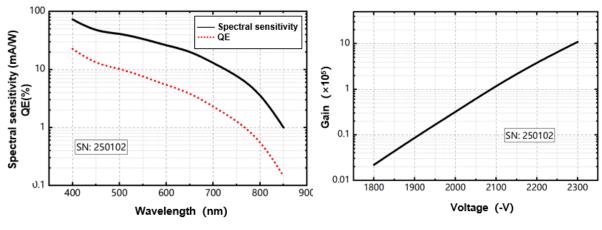

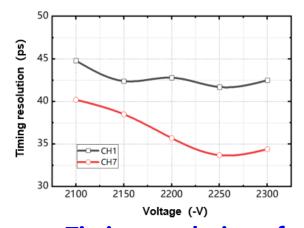

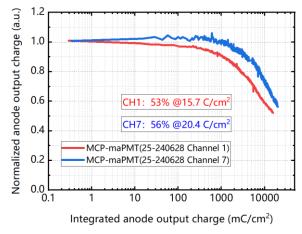

# Long lifetime MCP-maPMT

- MCP-maPMT: a critical component of the DTOF technology

- Intensive R&D on techniques (ALD and electron scrubbing) to produce long-life MCP-maPMT (target Q > 10 C/cm²).

- Designed and produced 1-inch MCP-maPMT prototypes with 16 annodes each.

- Carried out various tests of the MCP-maPMT prototypes

- TTS<40 ps, QE>20%, G>10<sup>6</sup>, Crosstalk < 7%

- Aging: <50% gain drop when Q>20 C/cm<sup>2</sup>

| 1  | 2  | 3  | 4  |

|----|----|----|----|

| 5  | 6  | 7  | 8  |

| 9  | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 |

| 218Hz  | 17Hz   | 5Hz    | 32Hz   |

|--------|--------|--------|--------|

| 1.3nA  | 0.22nA | 0.07nA | 0.22nA |

| 26Hz   | 3Hz    | 0.4Hz  | 5Hz    |

| 0.18nA | 0.07nA | 0.02nA | 0.1nA  |

| 17Hz   | 3Hz    | 1Hz    | 1Hz    |

| 0.38nA | 0.2nA  | 0.13nA | 0.11nA |

| 675Hz  | 27Hz   | 11Hz   | 12Hz   |

| 8.5nA  | 2.6nA  | 0.89nA | 0.53nA |

#### **Channel definition**

### Dark count & dark current

**Typical spectral response**

Timing resolution of different channels

**Output drop with IAC**

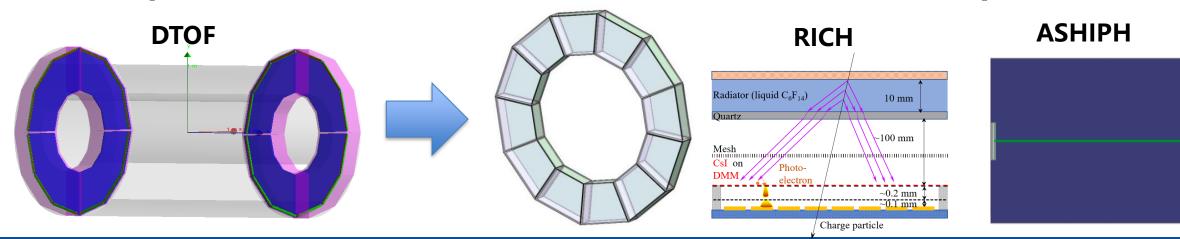

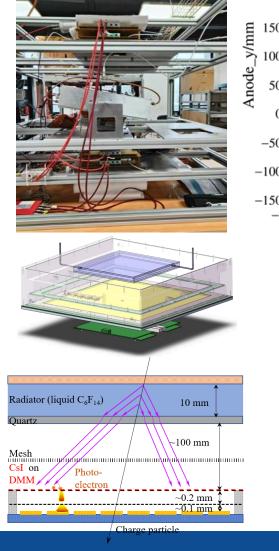

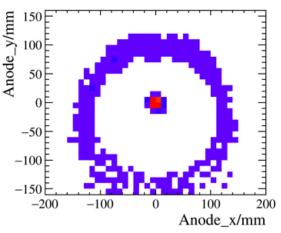

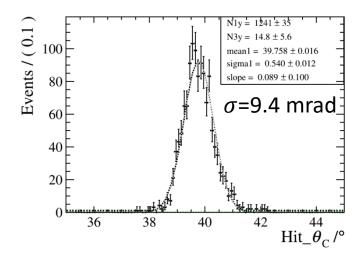

### **RICH Detector**

### Cosmic-ray test of a 32×32 cm<sup>2</sup> RICH prototype with both THGEM+MM and DMM

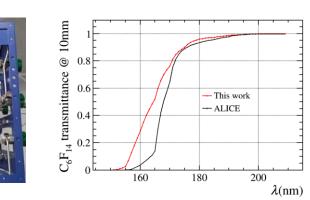

Purifying C<sub>6</sub>F<sub>14</sub> with good transmittance achieved

main issue: low photoelectron yield ~2pe/track.

QE of photo cathode needs to be improved!

DMM gain  $1.2 \times 10^5$ THGEM MM gain  $0.95 \times 10^5$

## **RICH Electronics**

- Completed the ASIC design and testing for the second-phase development.

- Test results show a ENC of better than 0.5 fC and a time resolution of better than 1 ns, meeting the design requirement.

- Based on the second-phase ASIC, a 1024-channel FEE prototype was designed.

- A beam test is ongoing with the detector at CERN's SPS

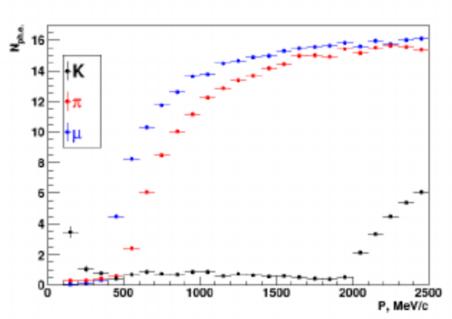

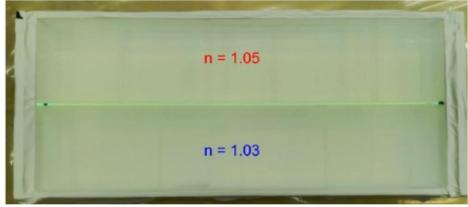

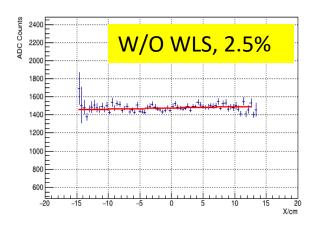

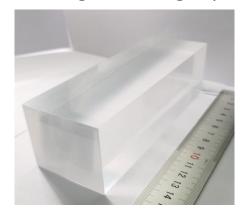

## **ASHIPH Detector**

- Ongoing effort by BINP to use ASHIPH (Aerogel, SHifter, Photomultiplier ) Cherenkov counter in STCF as a PID detector.

- Preliminary simulation showed a good pi/K separation up to 2 GeV/c.

- A prototype was built and tested recently.

PID performance with threshold of 1 phe

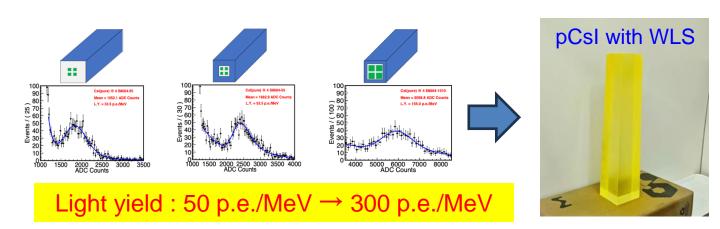

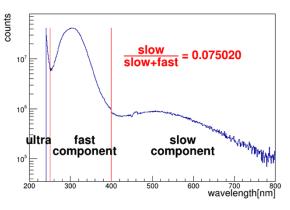

## **Electro-Magnetic Calorimeter: EMC**

- A crystal calorimeter using pCsl (short decay time of 30ns) to tackle the high background rate (~1 MHz/crystal)

- Crystal size: 28cm (15X<sub>0</sub>), 5×5cm<sup>2</sup>

- Defocused layout: 6732 crystals in barrel, 1938 crystals in endcaps

- 4 large area APDs to address low light yield: 4×(1×1cm²)

A very low light yield of 3.6% for pCsI → a major R&D task : enhance the light yield of a pCsI unit

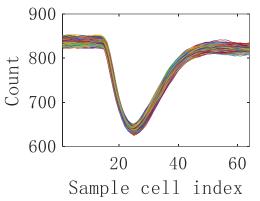

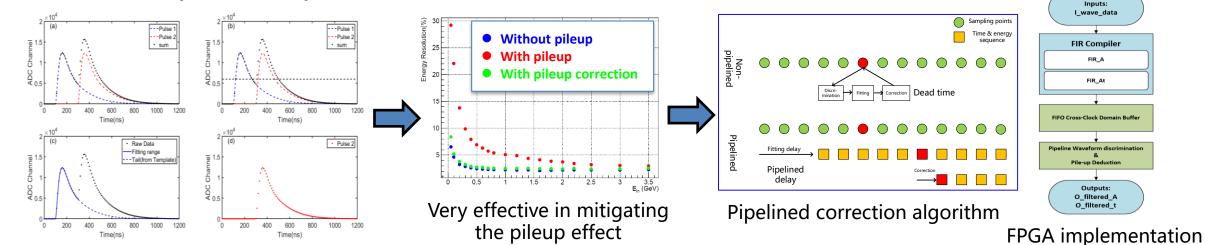

## **EMC:** Pileup Mitigation and Electronics

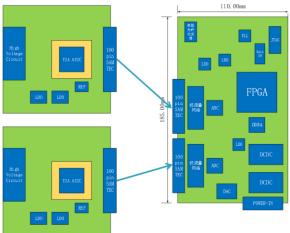

■ Significant pileup in EMC in the presence of beam background (~1 MHz/ch). A dead-time free pileup correction algorithm involving waveform fitting based on pipelined optimal filtering has been developed and implemented in FPGA

Development of waveform digitization electronics (CSA + ADC)

- The dynamic range was improved while maintaining the noise level of the high-gain channel.

- FEM adjustment for waveform consistency between high and low gain channels.

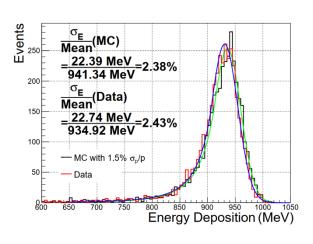

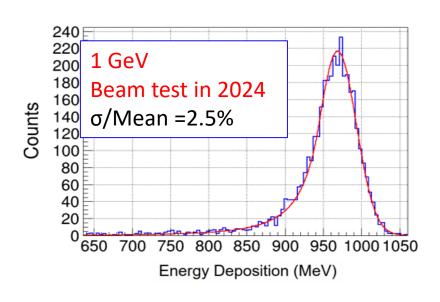

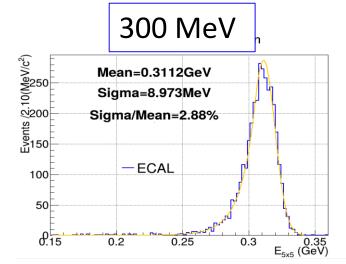

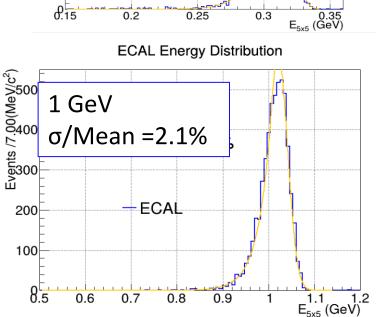

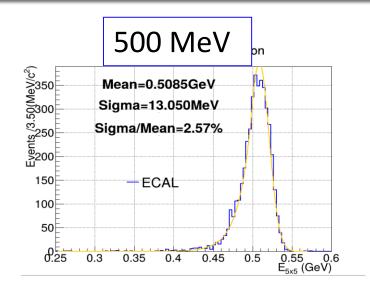

## 5×5 pCsl EMC Prototype

#### A pCsI EMC prototype

#### Performance from a beam test at CERN PS with 1 GeV/c electrons

### **Light collection uniformity Study**

### Optimizing the growth process of pCsI

The long wavelength part ratio could be lower than 10%

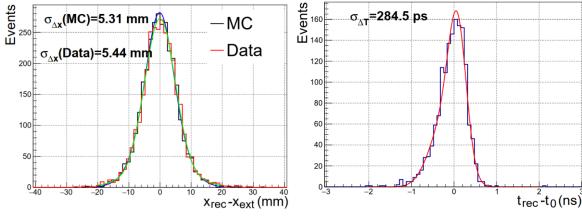

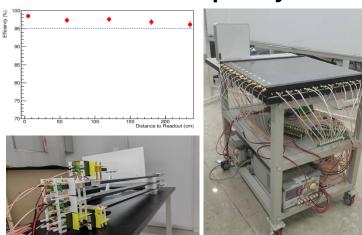

### MUD R&D

#### Scintillator strip + WLS + SiPM

- Design and fabrication of the scintillator unit: reflector, fiber groove, optical coupling, surface processing.

- Fabricated 2.4m long scintillator units (efficiency>95%) and a 50×50 cm<sup>2</sup> scintillator strip array

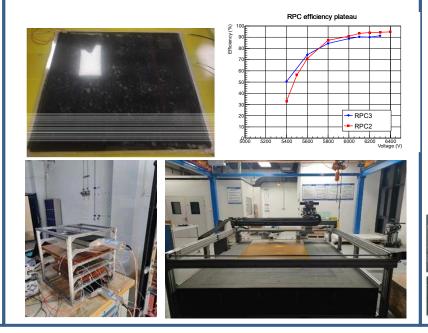

#### **Glass RPC**

- Developed glass RPC fabrication techniques.

- Built small RPC prototypes

(42×30 cm²) with low-resistivity

glass (1.5×10<sup>9</sup> Ω×cm) for high

count rate capabilities. (Under test)

- Larger 140×40 cm<sup>2</sup> prototypes are being built.

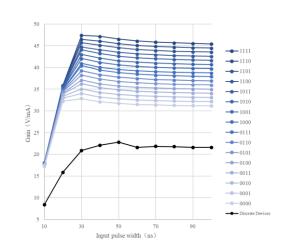

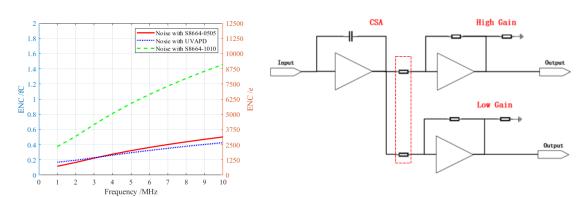

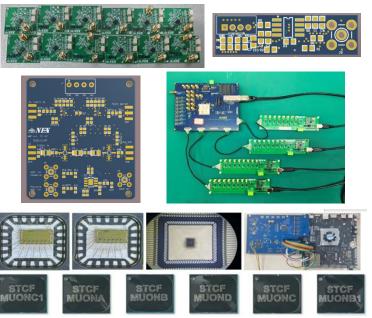

#### **Readout Electronics**

- Developed front-end amplifiers and readout boards. Tested with detector prototypes.

- Designed front-end ASICs for different input capacitance and gains. Prototype chips being tested

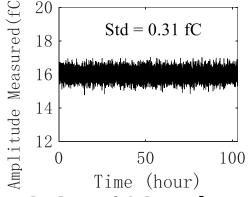

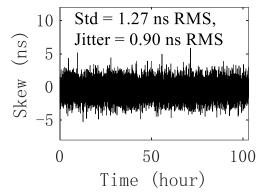

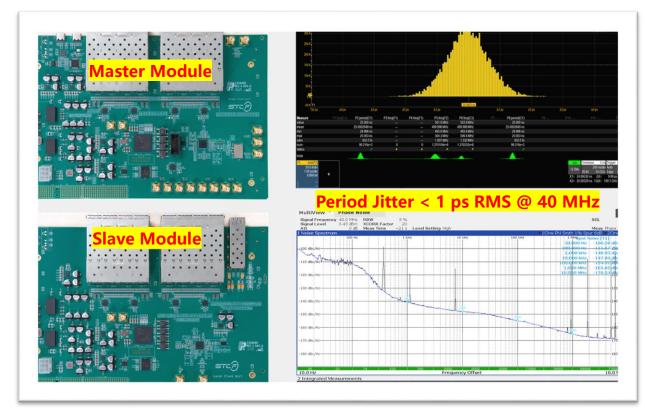

### **Clock and Data Transmission**

- Clock distribution system provides precise and stable clock signals with jitter < 5ps RMS</li>

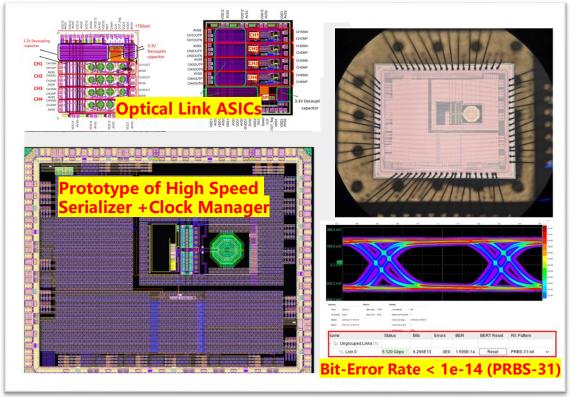

- High-speed serial data transmission: a GBTx-like ASIC, ADTC, uplink ~5Gbps

- Completed the design and test of clock distribution modules in a "master-slave" architecture

- Clock jitter tested ~1ps RMS

- joined the upcoming combined beam test

Designed SerDes and clock managing modules in ADTC, and optical modules. Chips received and tested

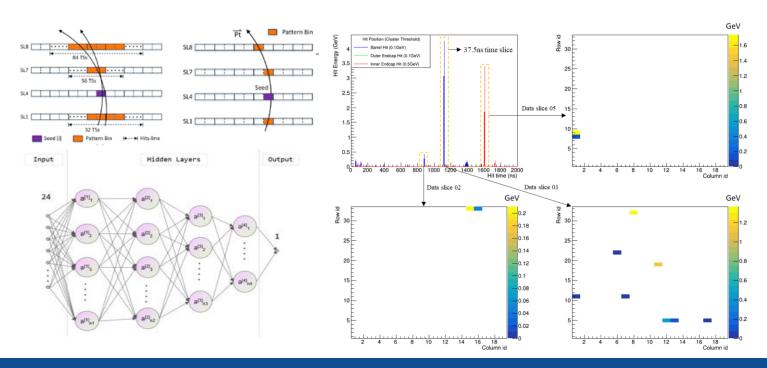

## **Trigger: Algorithms Studies and Development**

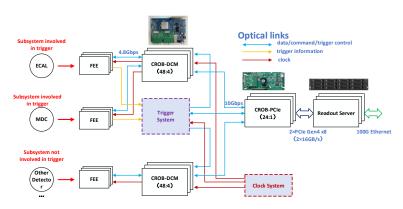

- STCF trigger scheme: L1 (MDC, ECAL and global trigger) + HLT

- L1-MDC trigger algorithms: 2D track reconstruction (track finding and parameters (pt,  $\theta$ ,  $\varphi$ , t) estimation) using pattern matching, 2D short-track reconstruction incorporating stereo layers using NN, Z impact parameter estimation using NN

- L1-ECAL trigger algorithms : overlapping events resolving, cluster reconstruction and splitting (E,  $\theta$ ,  $\phi$ , t)

- L1 global trigger: track and cluster matching, event T0 estimation, trigger menus for charged and neutral channels

- HLT: currently focusing on MDC HLT aiming to remove noise hits and reduce event size

#### Background trigger rate < 30 kHz

| Trigger channel       | Physics signal                                                                          | Energy point | Background trigger rate(kHz) | Signal trigger rate |

|-----------------------|-----------------------------------------------------------------------------------------|--------------|------------------------------|---------------------|

|                       | J/psi -> inclusive                                                                      | 3.097GeV     | 26.5                         | 98.2%(99.0%)        |

|                       | e*e* -> π*π*J/psi<br>Jpsi -> e*e*                                                       | 4.26GeV      | 18.9                         | 99.4%               |

|                       | $e^+e^- \rightarrow \pi^+\pi^-J/psi$<br>$Jpsi \rightarrow \mu^+\mu^-$                   | 4.26GeV      | 27.4                         | 99.8%               |

|                       | $e^+e^- \rightarrow \tau^+ \tau^-$                                                      | 4.26GeV      | 22.8                         | 98.7%               |

| Charged               | $e^+e^- \rightarrow \pi^+\pi^- J/psi$<br>$J/psi \rightarrow \Lambda \overline{\Lambda}$ | 3.097GeV     | 18.5                         | 99.3%               |

| channel               | $e^+e^> \pi^+\pi^-J/psi$<br>$J/psi -> \Xi \Xi$                                          | 3.097GeV     | 26.0                         | 99.1%               |

|                       | e+e> K+K-J/psi<br>J/psi-> 1+1-                                                          | 4.682GeV     | 18.7                         | 99.9%               |

|                       | $e^+e^- \rightarrow D_0 \overline{D_0}$                                                 | 3.773GeV     | 25.2                         | 100%                |

|                       | e+e> D+ D-                                                                              | 3.773GeV     | 19.3                         | 100%                |

|                       | $e^+e^- > D_s^+D_s^-$                                                                   | 4.04GeV      | 26.7                         | 100%                |

|                       | J/psi-> gam invisable                                                                   | 3.097GeV     | 24.8                         | 99.4%               |

| Neutral               | e*e>n nbar                                                                              | 3.097GeV     | 25.5                         | 97.6%               |

| channel               | e⁺e⁻-> gam n nbar                                                                       | 3.097GeV     | 26.0                         | 98.2%               |

|                       | e*e*-> gam n nbar(ISR)                                                                  | 3.713GeV     | 27.3                         | 98.4%               |

| Luminosity<br>monitor | Bhabha Scattering                                                                       | 4.26GeV      | 0.63%                        | 97.8%               |

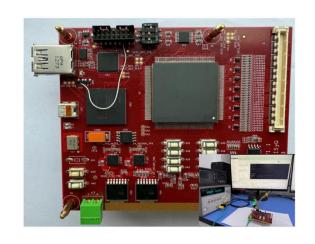

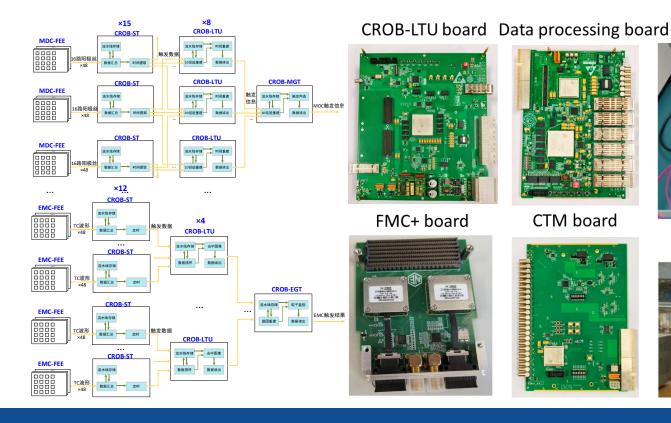

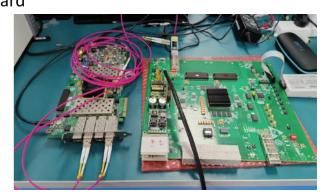

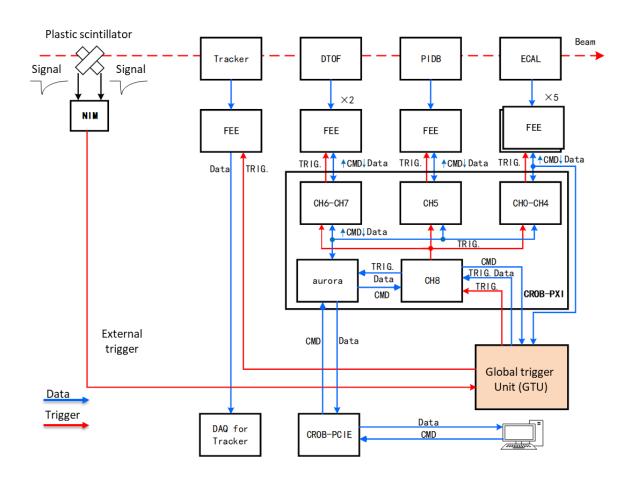

# Trigger: Hardware Development

- Design of trigger hardware architecture. Development of various core trigger hardware components (CROB-ST, CROB-LTU, CROB-MGT/EGT, CTM, FMC ...) . FPGA implementation of L1 trigger algorithms.

- A prototype L1 trigger system has been designed and built to demonstrate the trigger system design and its performance. An event simulator has been developed to generate pseudo data for the prototype trigger system.

- The prototype system has participated in the recent combined beam test at CERN

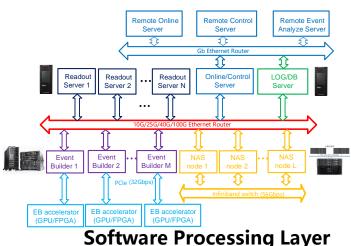

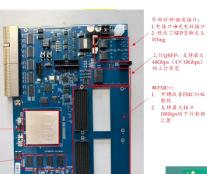

## **DAQ Design and Development**

核套DDR

- System architecture based on Data-Matrix: flow processing, heterogeneous computing, standard interfaces and protocols, global pipeline

- Core electronics boards design completed: CROB-PXI V3.0, CROB-PCIe V2.0, FMCP optical interface board

- Software and firmware development completed

- System testing and performance evaluation using simulation data

- A prototype DAQ system has participated in multiple combined beam tests

**FPGA Processing Layer**

**CROB-PXI** board

FPGA及风扇

**FMCP** optical interface board

**CROB-PCIe** board

Test of event building

- 12 rack servers

- 9 servers: readout+ 4 event builders

- 3 servers: 4 event builders

- 33 simulated data sources

- 17 big-frame sources: 20~32kB/frame

- 16 small-frame source: 135 Byte/frame

- Software optimization

- event building rate: 20 kHz → 90kHz

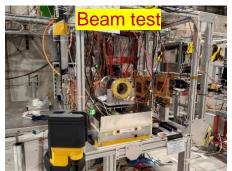

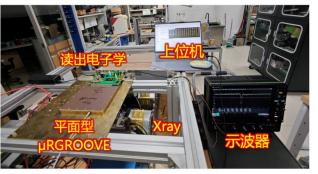

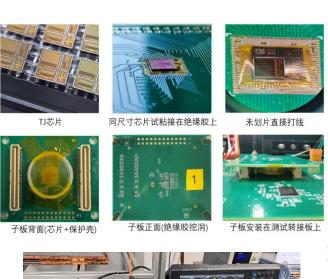

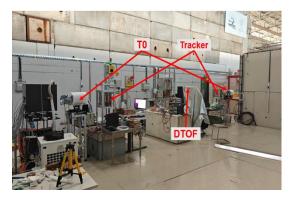

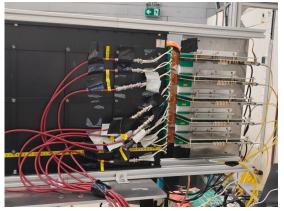

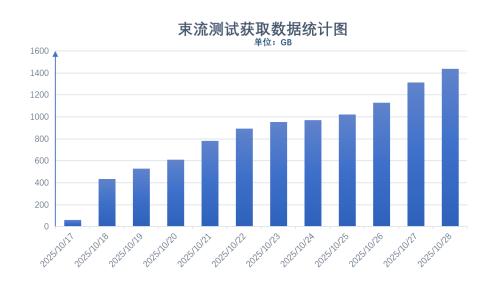

## **Second Combined Beam Test**

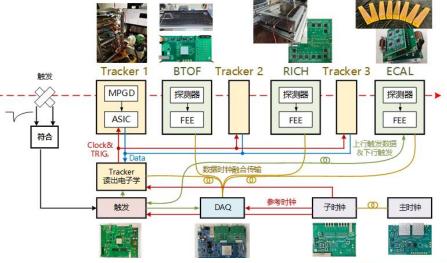

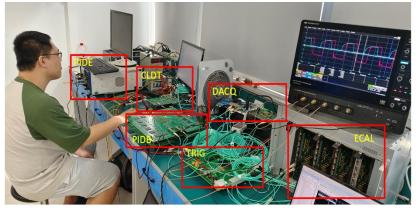

Launched the second test beam campaign this year for a large combined system (ITK, RICH, BTOF, EMC, Clock, Trigger, DAQ)

**Laboratory test**

CERN PS T9 in Oct. 2025

## Trigger and DAQ in Beam Test

- Full trigger chain verified with GBT link to RICH, ECAL and DAQ implemented

- high ECAL triggering efficiency achieved with a latency of 1.3 μs

- DAQ worked well with a total data volume of 1.4 TB accumulated

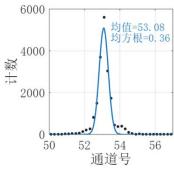

## **ITKM Preliminary Results**

- Track reconstruction and data analysis based on the Corryvreckan software

- · Preliminary results on the detection efficiency, spatial and timing resolution

#### CharTPix-130nm

- Efficiency higher than 99% at low thresholds and remains high at higher thresholds

- Spatial resolution: ~50 (10) um in the long (short) pitch

- Timing resolution ~60ns

- Efficiency higher than 98% at low thresholds and drops quickly

- Spatial resolution: ~7um

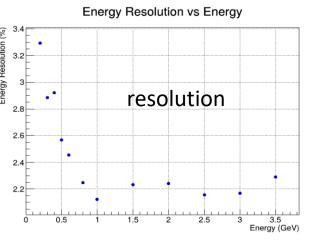

## **ECAL Preliminary Results**

- Tested using electrons with energy ranging from 200 MeV to 3.5 GeV

- Good energy resolution achieved

Data analysis is ongoing. More results will come out soon for other detectors

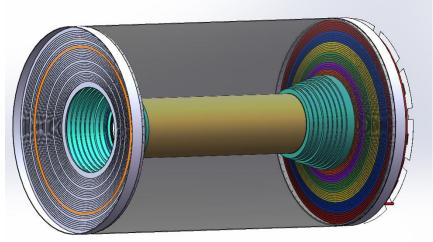

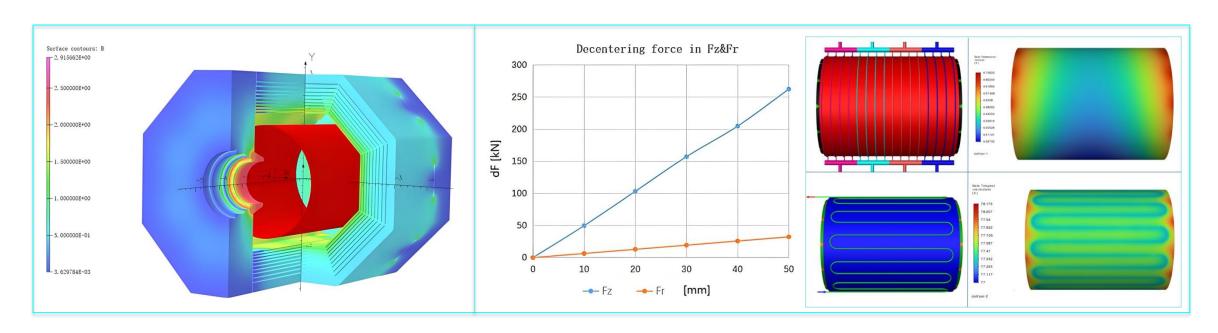

# Superconducting Solenoid Magnet

- Optimized the physics design of the magnet by performing FEA of magnet field and decentering forces.

- Studied impact of inhomogeneity of the magnetic field on tracking performance and solutions for shielding stray magnetic fields.

- Designing the magnet support structure using carbon fiber. Investigating heat leakage issue.

- Studying cryogenic forced flow (77K)and thermosiphon (4.2K) schemes with FEA.

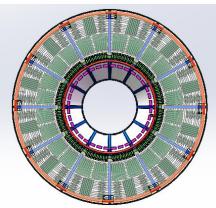

## **Detector Mechanical Design**

- **■** Detector conceptual design has been transferred into engineering drawings

- **Engineering design available for each sub-detector or system**

- **■** Design studies on detector assembly and installation

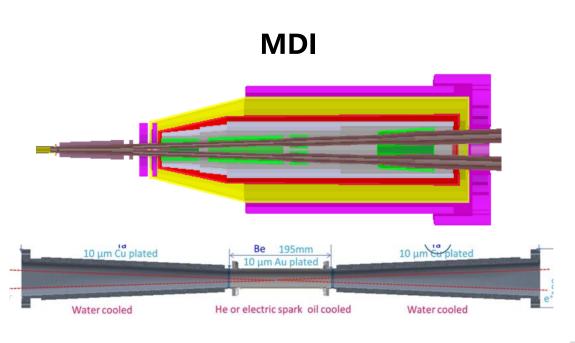

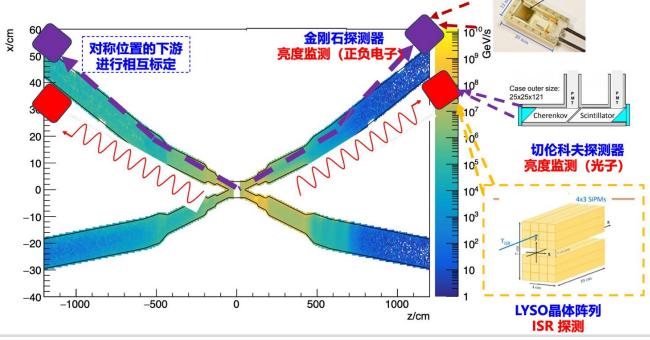

## Beam Background and Forward Detectors

- Keeping up with accelerator design evolution for beam background estimation. Working closely with MDI people to optimize the detector geometry and radiation shielding design in MDI region.

- Simulation studies on luminosity detectors (radiative Bhabha) and zero-degree detectors (ISR, two-photon process). Preliminary determination of the sites of these detectors at STCF from these studies.

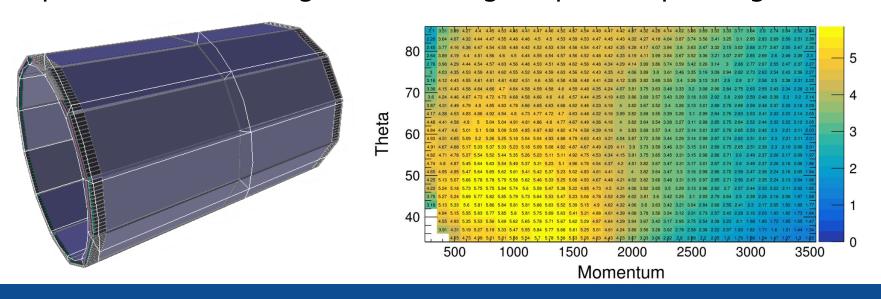

### **STCF Detector Performance with Full Simulation**

#### **Tracking efficiency**

#### **EMC** energy resolution

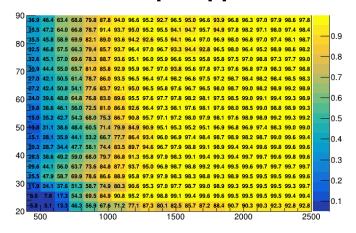

#### Muon ID eff. @ pi suppression=30

eff.  $\sim$  > 90% when p  $\sim$  >1GeV/c

#### **EMC** position resolution

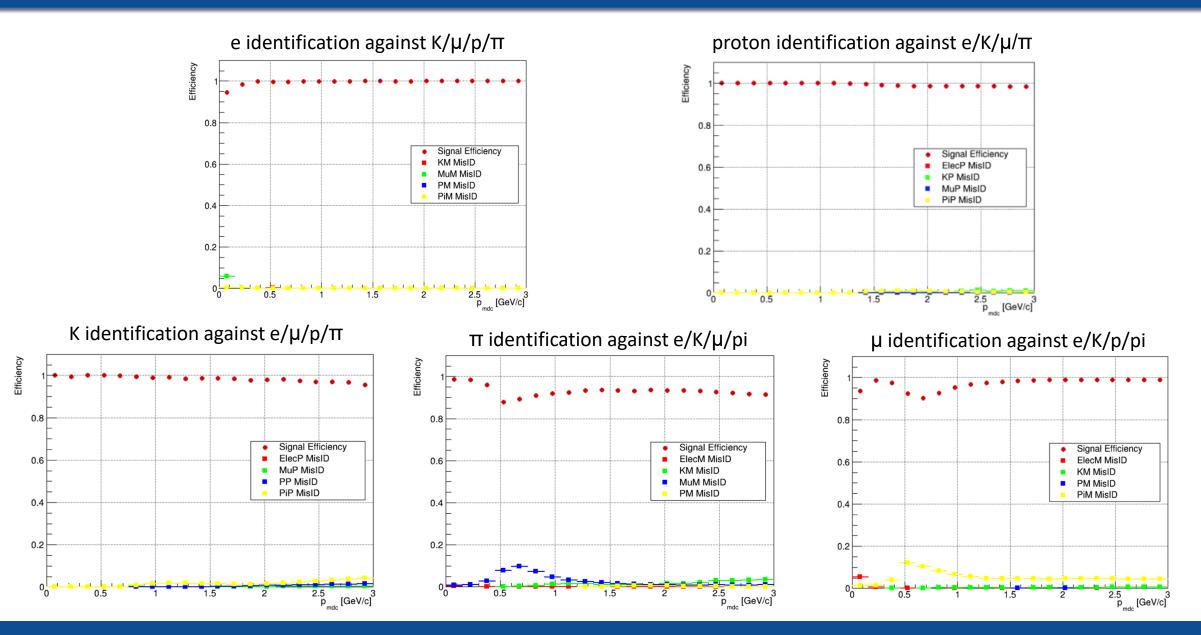

### **Global PID Performance**

### **Final Remarks**

- A very comprehensive STCF detector R&D project has taken shape and is being vigorously executed.

- Enormous progress has been made in many aspects of the project and on many sub-detectors or systems. Some sub-detectors have reached the large-scale prototype level.

- A beam test at CERN of a fully integrated system of EMC + BTOF + RICH+ Clock

+ Trigger + DAQ has been conducted at CERN this October.

- Detector performance has been evaluated with full simulation and can meet physics requirements. Many sub-detectors have been optimized with full simulation. More are underway to further enhance the detector capability.

- International collaboration has been expanded and substantiated (LHCb-TORCH, BINP-ASHIPH/MDC), and continues to be an important goal of STCF.

- STCF detector TDR is in preparation and will come out soon.