Chinese Academy of Sciences

# An interface RTM board for HEPS timing based on MicroTCA.4

#### Jin Zhang<sup>1</sup>, Chenyan Lu<sup>1</sup>, Fang Liu<sup>1</sup>

1 Institute of High Energy Physics, Chinese Academy of Sciences

An interface RTM board for HEPS timing based on MicroTCA.4 | 2024 MicroTCA/ATCA Sep.19 Hefei China

- Introduction of HEPS Timing System

- **RTM Management and Circuit Design**

- a. Circuit Design

- **b.** Architecture of RTM management

- c.  $I^2C$  control and Power management

- d. Test

- Summary

An interface RTM board for HEPS timing based on MicroTCA.4 | 2024 MicroTCA/ATCA Sep.19 Hefei China

#### Introduction

### **HEPS**

HEPS (High Energy Photon Source):

- One of the brightest 4th synchrotron radiation light sources

- > 6GeV storge ring ,500MeV linear accelerator, booster

| booster h long beamline                                                            | Main param                                                       | eters of HEPS      |  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------|--|

| linac                                                                              | Beam energy[GeV]                                                 | 6                  |  |

| storage ring and<br>experiment hall<br>laboratory building<br>guest house building | Circumference[m]                                                 | ~1360              |  |

|                                                                                    | Emittance[nm.rad]                                                | 0.06               |  |

|                                                                                    | Beam current[mA]                                                 | 200                |  |

|                                                                                    | Cell Units                                                       | 48                 |  |

|                                                                                    | Injection                                                        | Тор-ир             |  |

|                                                                                    | Brightness[phs/s/mm <sup>2</sup> /<br>mrad <sup>2</sup> /0.1%BW] | > 10 <sup>22</sup> |  |

Fig 1 HEPS Facility Map<sup>1</sup>

[1] https://www.hplpb.com.cn/article/doi/10.11884/HPLPB202234.22008

#### Introduction

### **HEPS Timing System**

- HEPS Timing system based on MicroTCA.4

- The precision requirement of the HEPS timing system:

- a. General jitter between RF and trigger should be less than 30ps, and the jitter of SR kicker should be less than 10ps

- b. Some delay modules need an adjustment precision of 10ps specially

- The function of timing system

- a. The timing system needs to distribute trigger signals for BI system, Linac station, Booster station, power supply, etc

- b. We have a requirement of more EVR outputs

PICMG® Specification MTCA.4 R 1.0 Draft 0.7d AMC, μRTM and μTCA Shelf for Physics

#### Introduction

### **HEPS Timing System**

- Specific Objectives(Why are we doing this board?)

- Insufficient output on the front panel

- > Cost

- Different types of interfaces(BPM, Optic, E-gun, Power etc.)

- Flexible and efficient to change

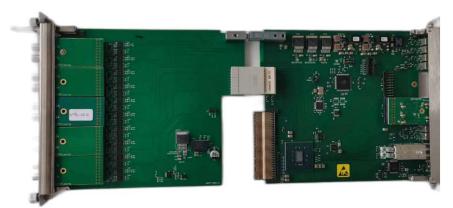

- The structure we used:

- Rear insert structure

- Miniature board structure

#### **Architecture of RTM Circuit**

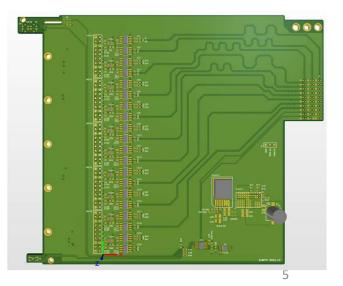

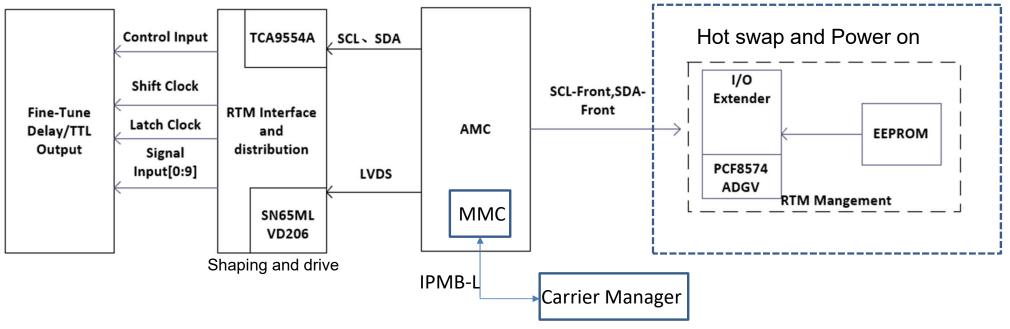

**RTM circuit includes:** RTM management  $I^2C$  control Voltage conversion Output module Zone 3 Zone3 connector Connector output **5**V Voltage +12V conversion 3.3V Signal input 3.3V LVDS to single **FPGA** SDA, SCL I/O Extender SDA-Front, SCL-Front MMC FRU Backplane **EEPROM** Power management FRU AMC handle RTM

### **Circuit Design**

- The FPGA provides ten differential signals, which are distributed through the output circuit

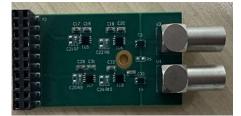

- We have designed four different output boards for different applications

- > Fine-tune delay module: the delay adjustment range is about 10ns, the adjustment accuracy is 10ps

- > 5V /3.3VTTL output module: applied for beam diagnostic devices and output jitter less than 30ps

- > Optic module :applied to the isolation of high-voltage pulse equipment such as power supply

Figure Fine-tune delay module

Figure 5V TTL output module

Figure 3.3V TTL output module

Figure Optic module

Figure The Rear-Transition Module for trigger distribution

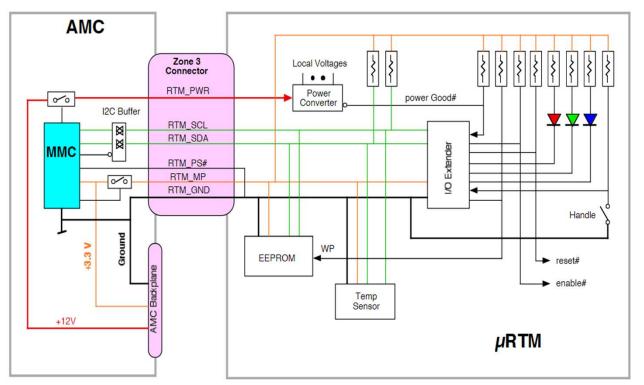

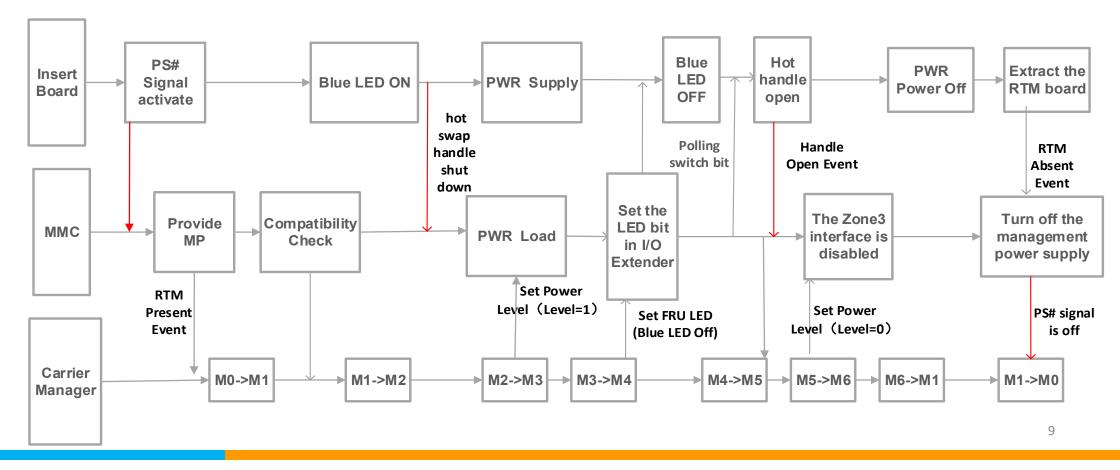

#### **Architecture of RTM management**

#### Zone3 Connector

- Interface : PS# ,Ground, Management

Power, I<sup>2</sup>C bus and Payload Power

- I/O extender: detect the hotswap handle position and drive three LED's

- AMC-RTM connector standardized with IPMI Management Power from AMC to RTM

- Low-jitter clock lines, point-to-point connections, interlock summing

- RTM hot-swap feature same as AMC

Figure 2 AMC/RTM Management Block Diagram

#### Management

#### RTM Insertion and Extraction

MMC needs to acquire the status of handle actively

## $I^2C$ control

- $I^2C$  control :

- SDL-Front, SCL-Front (Power on and hot swap in RTM)

- SDL, SCL (Control delay module)

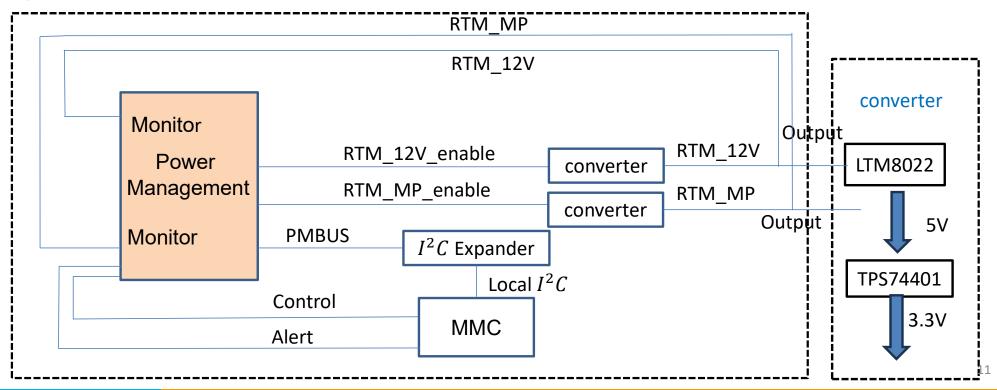

#### **Power Management**

**Power Management**

- MP (3.3V) is supplied directly from the front AMC

- > After the board is correctly inserted and compatibility checked, the load power supply (12V) is enabled

- Voltage converter

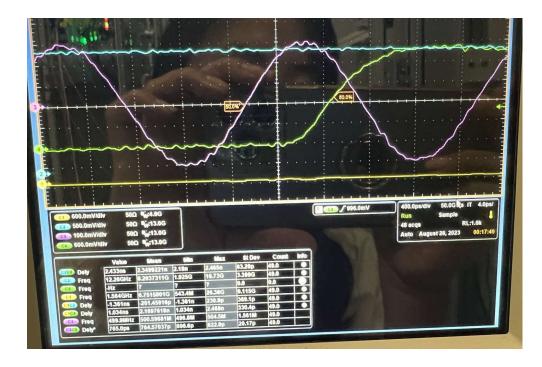

# Test

- 5V TTL Jitter: 5.71ps

- Point: 1.4k

- Already applied to HEPS

- Red signal is from reference line

- Green signal is the trigger for BPM

- RMS jitter 29.17ps

#### Test

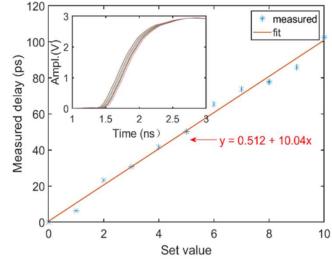

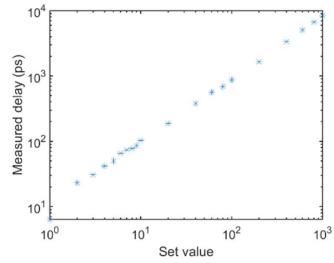

- Fine-tune Delay Test

- During testing, set the first channel as the reference signal

- Perform delay adjustment, change the amount of delay ,The delay adjustment is performed by adjusting the delay step size of the delay module in the EVR. For each delay value, 1000 waveforms are measured with an oscilloscope and averaged over the 1000 sets of data.

Figure 10ps step size adjustment 10 times, adjust 100ps

Figure 10ps delay step size, adjustment close to 10ns

### Summary

- An RTM rear board circuit based on Micro TCA.4 event timing system is developed for signal distribution

- Combined with the specific application requirements of HEPS, we independently developed a 5V/3.3V TTL module, which is suitable for beam measuring equipment

- The module with a delay adjustment range of about 10ns and adjustment accuracy of 10ps is developed, which is mainly used for EVR output and scenes requiring precise adjustment

- For high-voltage pulse equipment, isolation design of the trigger signal is carried out, and we develop an isolation optical module